A Moore-törvény évtizedeken keresztül meghatározta a félvezetőipar fejlődését, kimondva, hogy körülbelül kétévente duplázódik az integrált áramkörök tranzisztorszáma. 2026-ban azonban az elektronikai ipar olyan korlátokhoz érkezett, amelyek megkérdőjelezik a fizikai lehetőségeit ennek a tempónak. Az iparág két kiemelkedő technológiai újítása, a 3D-s chipek és a komplett vertikális tranzisztorarchitektúra (CFET) új perspektívába helyezi a számítási teljesítményt, és lehetővé teszi a Moore-törvény életben tartását. Cikkünkben alaposan áttekintjük, hogyan forradalmasíthatják ezen technológiák a jövő elektronikai eszközeit, és milyen kihívásokkal kell szembenézniük a piacra lépés során.

A Moore-törvény jelentősége és kihívásai 2026-ban

A Moore-törvény nem csupán technikai jóslat, hanem az informatikai fejlődés egyik sarokköve. Az, hogy az integrált áramkörök tranzisztorainak száma kétévente megduplázódik, meghatározza az innováció, a teljesítmény és a gazdasági növekedés ütemét is. Egyre gyorsabb, kompaktabb és energiatakarékosabb eszközök készültek, amelyek forradalmasították életünket az okostelefonoktól a szuperszámítógépekig.

Az utóbbi években azonban a csíkszélesség csökkentése egyre problémásabbá vált. A 2 nanométeres és annál kisebb eljárásoknál a kvantumhatások és az elektromos zaj jelentős teljesítménycsökkenést és komplexitást okoznak, ami a folyamatok további miniaturizálását fizikailag és gazdaságilag is megnehezíti. Ez azt eredményezte, hogy az ipar vezetői a 3D-s chipek és a vertikális tranzisztorok, például a CFET technológiák irányába fordultak.

2026-ban a Moore-törvény már nem csupán a tranzisztorméret csökkenésén alapul, hanem a chipek architekturális és interkonnektív fejlődésén is. A háromdimenziós integráció és a teljesen vertikális tranzisztorarchitektúrák lehetővé teszik, hogy újra pörgésbe lendüljön az innovációs ciklus – mindez azonban új típusú mérnöki, gyártástechnológiai és piacstratégiai kihívásokat is magával hoz.

3D-s chipek fejlődése: Új dimenziók a teljesítményben

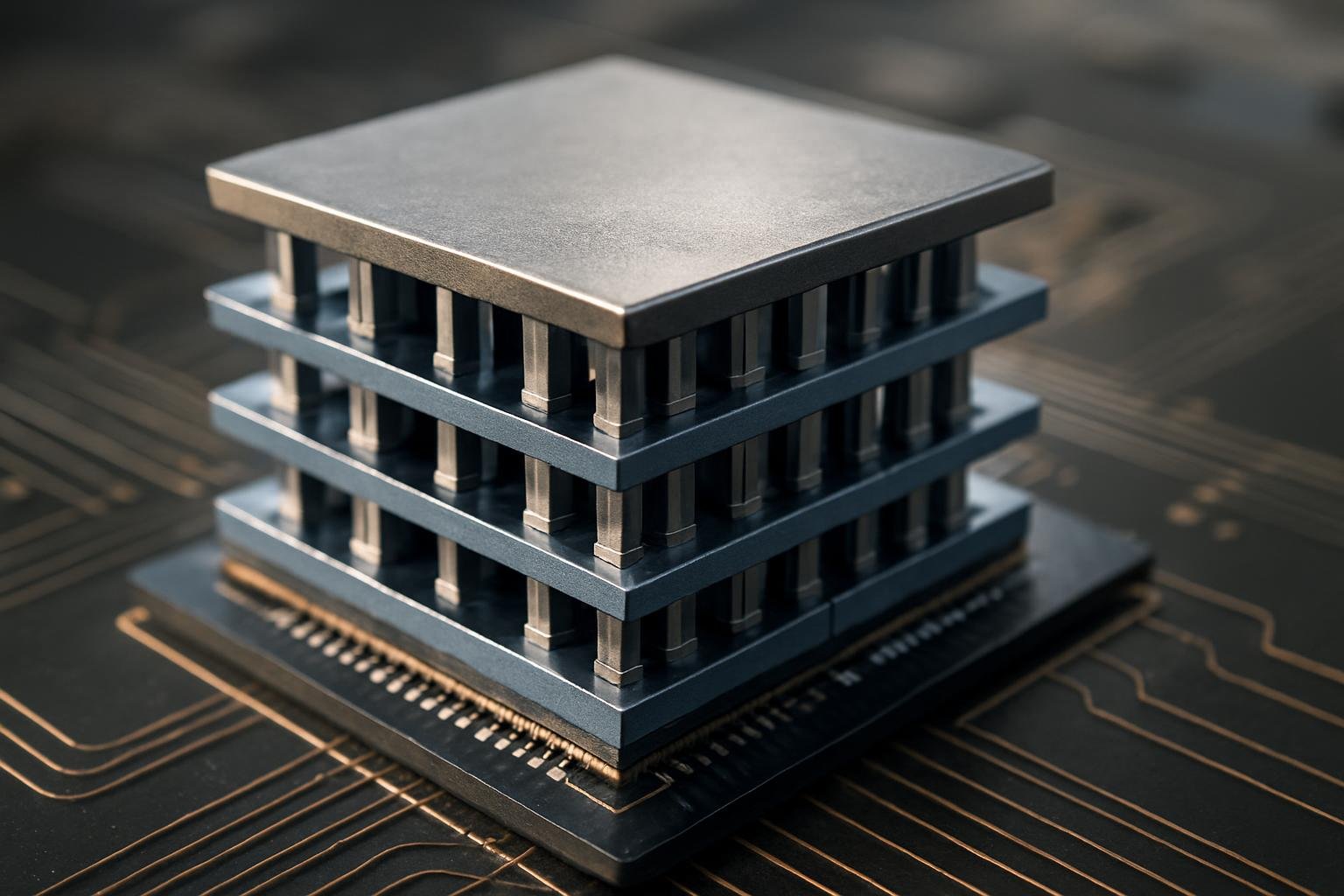

A 3D-s chipek, vagyis a vertikális integrált áramkörök, napjaink egyik legrugalmasabb és legizgalmasabb architektúrái. Az alábbiakban összefoglaljuk a fejlődésük főbb fázisait és előnyeit:

- Rétegezés és stacking:

A 3D-s chipek lényege, hogy több logikai és memória réteget helyeznek egymásra, ezzel jelentősen növelve a tranzisztorsűrűséget anélkül, hogy a chipek alapterülete nőne. - Rövidebb jelutak:

Az egymásra helyezett chipek közötti kapcsolatok (TSV-k, azaz Through-Silicon Via-k) minimálisra csökkentik a jelutakat és késleltetéseket, gyorsabb adatáramlást lehetővé téve. - Moduláris felépítés:

A különböző funkciók (processzor, memória, AI modulok) külön rétegként jelenhetnek meg, és a gyártók rugalmasabban fejleszthetnek új megoldásokat.

E megközelítéseknek köszönhetően a 3D-s chipek teljesen új lehetőségeket kínálnak a teljesítménynövelésre és az energiahatékonyság javítására is. Jelenleg a legfejlettebb okostelefonokban, szerverekben és szuperszámítógépekben is kezdenek megjelenni ezek a megoldások, de 2026-ra ez a technológia várhatóan széleskörű standard lesz az elektronikai iparban.

Vertikális tranzisztorok (CFET): Innováció a nanométeren túl

A vertikális tranzisztorok, különösen a CFET (Complementary FET) struktúrák, új korszakot hoznak a tranzisztortechnológiában. Mivel a hagyományos FET-ek síkban helyezkednek el, a további méretcsökkentés egyre nehezebb. A CFET ezzel szemben vertikálisan, egymás fölé helyezve tartalmazza az n- és p-csatornás tranzisztorokat. A technológia főbb újításai:

- Egymásra helyezett tranzisztorok:

Az nFET és pFET tranzisztorok közvetlenül egymás felett helyezkednek el, ami drámaian csökkenti az egy tranzisztorra jutó alapterületet. - Alacsonyabb energiafogyasztás:

A rövidebb csatornahossz és a kompakt felépítés miatt kevesebb energia szükséges a kapcsoláshoz. - Könnyebb skálázhatóság:

A vertikális felépítés jobban tolerálja a kvantumhatások és gyártástechnológiai kihívások miatti problémákat, mint a síkbeli architektúrák.

A CFET technológia már most is intenzív kutatás-fejlesztési fázisban van, és az előrejelzések szerint 2026-ban az első kereskedelmi alkalmazásaik is megjelenhetnek. Ez a fejlesztés hosszú távon jelentősen befolyásolja majd, mennyire és meddig tartható életben a Moore-törvény a félvezetőiparban.

3D-s chipek és CFET technológia előnyei és hátrányai

A 3D-s chipek és CFET technológia alkalmazása számos előnyt kínál, de komoly kihívásokkal is szembesül az ipar:

Előnyök:

- Jelentős teljesítménynövekedés:

A chipeken belüli rövidebb utazási idők és a rétegezett struktúra gyorsabb számításokat eredményez. - Energiahatékonyság:

Az áramkörök közötti kisebb távolságok miatt csökken az energiafogyasztás. - Kompakt dizájn:

Több funkció, kisebb helyen – az eszközök kisebbek és könnyebbek lehetnek.

Hátrányok:

- Gyártási komplexitás:

Az egymásra épülő rétegek és vertikális tranzisztorok gyártása különlegesen magas precizitást igényel. - Hűtési problémák:

A 3D-s chipek rétegei között nehezebb a hőelvezetés, ami tervezési kihívásokat okozhat. - Nagyobb költségek:

Az új technológiák bevezetése jelentős beruházást és komolyabb ellátási láncot kíván.

A következő években várható, hogy a mérnökök és kutatók újabb anyagok, innovatív hűtési megoldások és gyártási technikák révén tovább javítják e technológiák hatékonyságát és elérhetőségét.

Piaci hatások és alkalmazási területek 2026-ban

A 3D-s chipek és CFET technológiák piaci hatása várhatóan jelentős lesz 2026-ban. A legfontosabb területek, ahol ezek a fejlesztések áttörést hozhatnak, a következők:

- Mesterséges intelligencia és gépi tanulás:

A 3D-s architektúrák párhuzamos adatfeldolgozási lehetősége ideális a masszívan párhuzamos AI-feladatokhoz. - Mobil- és hordozható eszközök:

A kisebb méretű, mégis nagyobb teljesítményű chipek lehetővé teszik a vékonyabb, energiatakarékosabb eszközök fejlesztését. - Adatközpontok és felhőszolgáltatások:

Nagyobb sűrűségű chipek révén csökkenthető a szerverparkok fizikai mérete és energiaigénye.

Emellett a 3D-s chipek és CFET megoldások szerepet kapnak majd az autóiparban (önvezető rendszerek), egészségügyi technológiákban és a nagy sebességű kommunikációs hálózatokban is. A piaci alkalmazkodás azonban kihívást jelenthet a gyártási költségek és a technológiai komplexitás miatt, így várhatóan először a csúcskategóriás eszközökben terjednek el.

Gyakori kérdések a 3D-s chipekről és vertikális tranzisztorokról (10)

- Mit jelent pontosan a 3D-s chip?

- Olyan mikrochip, amely rétegekben, egymás fölé integrált áramköröket tartalmaz.

- Mi a CFET technológia lényege?

- Vertikálisan egymás fölé helyezett, n- és p-csatornás tranzisztorokból álló architektúra.

- Mennyire elterjedtek 2026-ban ezek a technológiák?

- Főként csúcskategóriás termékekben, adatközpontokban és AI-eszközökben jelennek meg először.

- Mit jelent a TSV (Through-Silicon Via)?

- Olyan furat, amely összeköti a 3D-s chip rétegeit fizikai és elektromos értelemben.

- Jobban melegednek-e a 3D-s chipek?

- Igen, a hőelvezetés bonyolultabb, de speciális hűtési megoldásokkal kezelhető.

- Milyen előnyei vannak az energiahatékonyság szempontjából?

- Rövidebb jelutak és kisebb kapcsolási energiaigény.

- Mekkora befektetést igényel ezeknek a chipeknek a gyártása?

- Jelentős tőkét és innovatív gyártási infrastruktúrát.

- Összeférhetők-e a meglévő gyártási szabványokkal?

- Számos új gyártástechnológiai lépést és komponens fejlesztését követelik meg.

- Milyen hosszú élettartammal lehet számolni?

- Hasonló vagy akár jobb a hagyományos síkchipekhez képest, de a hőkezelés kritikus.

- Jelenthetnek-e ellátási lánc szűk keresztmetszetet?

- Igen, az új anyagok és eszközök bevezetése kihívásokat jelent az ellátási láncban.

2026-ban a Moore-törvény tovább él, még ha nem is a hagyományos úton. A 3D-s chipek és a vertikális tranzisztorok (CFET) bevezetése új korszakot nyit az integrált áramkörök világában: a funkcionalitás, a teljesítmény és az energiahatékonyság új, eddig nem tapasztalt szintjei válnak elérhetővé. Ugyanakkor ezek a forradalmi technológiák kihívások elé is állítják a mérnököket és a piacot, végső soron pedig minden felhasználót. Az azonban biztos, hogy a Moore-törvény szelleme új, kreatív formában még évekig életben marad az elektronikai iparban.